# SOUND/SPEECH MODULE AS-2518-61

### THEORY OF OPERATION

## I. SQUAWK & TALK (S & T) SELF-TEST

The S & T module has, as part of integrated circuit U5, a program designed to test the module each time power is turned on. No action is required on the operator's part to initiate the test. The program causes the  $\mu P$  chip to test itself (U1), the scratch pad memory (U6), each of the I/O chips (PIA's, U7 and U11), the sound generator chip (U12), and the speech generator chip (U8). If the  $\mu P$  chip finds all circuits in proper operating order it initializes the S & T module and makes it ready for sound effects. If the  $\mu P$  finds a fault during the course of Self-Test, it stops at that point in the test and does not allow game play.

The accuracy of the S & T Self-Test is about 90%. The S & T module catches all faults except D/A converters, voltage controlled amplifiers, power amplifier, speech PHROM and input interface problems.

The interesting idea behind the S & T Self-Test is that not only does it prevent sound generation when faults are detected, but like the MPU module it helps to localize these faults. The LED on the S & T module flashes once for each successfully completed test. Simply counting the number of flashes of the LED after power-up localizes the fault to the offending circuit of the module.

#### A) 1ST FLICKER

On Power-Up, the  $\mu$ P chip (U1) requires that  $+5\pm.25$ VDC be applied before the reset line is allowed to swing from  $\emptyset$  to +4.8VDC. If these conditions are met, and if the  $\mu$ P chip is good, the LED on the module flickers briefly. (approx. 300msecs.)

The reset circuit on the S & T module works with the +5VDC regulator VR1 to prevent the reset line from going high until the +5V supply has had time to stabilize after power on. At power on, C1 slowly charges via R1. The voltage across C1 is monitored by U15. When it reaches +1.7VDC, U15 takes the reset line high. U15 is a "Schmitt Trigger" device with a built-in hysteresis to prevent slowly changing inputs from causing multiple outputs. Diode CR1 across R1 provides a quick discharge path for C1 in the event that the +5V momentarily disappears.

If the LED stays on, the probable causes are: Faulty U5, faulty U15, leaky C1, open R1, leaky CR1, or faulty U17.

#### B) 1st FLASH

The  $\mu P$  chip (U1) next goes out to the NMOS RAM (U6). It attempts to write then read back all 256 patterns (00000000 to 11111111) in each of the 128 scratch pad RAM locations. If at any point in this test the  $\mu P$  fails to correctly read back a pattern that it has written, U6 is deemed defective and the  $\mu P$  will not allow sounds to be made. If the  $\mu$  completes the 256 X 128 = 32,768 tests successfully, it flashes the LED.

If the LED fails to flash the probable causes are: Faulty U6, faulty U15, or faulty U17.

#### C) 2nd FLASH

The  $\mu P$  chip (U1) now tests the first PIA chip, U7. Each of the two PIA chips, U7 and U11 are identical and interchangeable. The test for both is identical.

To determine if each of the two PIA chips are good, the µP chip does the following:

- 1) It tests each of the two full byte port initialization registers in a manner similar to that of U6.

- 2) It tests each of the two full byte I/O registers, PAØ-PA7, PBØ-PB7, in a similar manner to U6.

- 3) It then tests the CA2 and CB2 ports. The ports are initialized as outputs. The port is then written into to see if it can store a '1' and then a '0'. When both ports are found good, the µP flashes the LED.

### D) 3rd FLASH

The µP chip (U1) performs the same tests for U11 as it did for U7. It then flashes the LED.

### E) 4th FLASH

The  $\mu P$  chip (U1) performs a test similar to the test for U6 on the sound generator chip, U12. U12 is controlled through PIA, U11. If the sound chip passes all tests then the  $\mu P$  flashes the LED.

### F) 5th FLASH

The speech generator chip (U8) requires an initialization sequence on power-up. Since the speech chip is a 'slow' device, there is an acknowledgement signal from the speech chip to the  $\mu P$  (via PIA U7). Every time a write to the speech chip is performed, the speech chip responds with an acknowledgement. The  $\mu P$  attempts to send 9 bytes of initialization data to the speech chip, one at a time, waiting for the acknowledgement for each byte. If it is successful in doing this, the speech chip is deemed functional and the  $\mu P$  flashes the LED.

### G) SQUAWK & TALK INITIALIZATION

The  $\mu$ P (U1) now initializes the two PIA's (U7 and U11) and waits for an interrupt.

#### II. NORMAL OPERATION

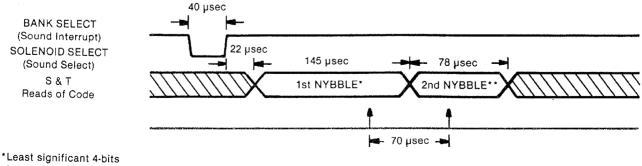

The S & T accepts address signals from the MPU to select one of the sound or speech signals stored in its memory. It then plays the request by controlling the sound generator chip (U12) or D/A converter (U10) for sounds, or the speech generator chip (U8) for speech. The S & T is notified of a sound/speech request by an interrupt from the MPU. This interrupt is generated by toggling the solenoid bank select signal on the MPU which is the sound interrupt input to the S & T. The code number of the sound/speech required is passed as two half-bytes (nybbles) over the MPU solenoid select lines which are the sound select inputs to the S & T. The current timing for this process is shown below.

\*\*Most significant 4-bits

Invalid code numbers are ignored by the S & T.

#### III. POWER SUPPLIES

The S & T requires two supplies for normal operation. A +12.0VDC @ 3A unregulated voltage is required for the LED, VR1, and U18 the audio power amplifier. The regulated +5VDC for all components is derived (via VR1) from this voltage. A full wave rectified 6.3 V voltage is required for VR2. The regulated -5VDC for the speech generator chip is derived from this voltage. CR7, CR8, C37 and C38 form a voltage doubler on the input of VR2. This insured sufficient negative voltage on VR2's input to meet the -7.5V requirement even at low line voltage.

#### IV. AUDIO CONTROL

The Squawk & Talk audio portion is made up of three sections: A speech channel, a sound channel, and a power amplifier. Speech and sound signals are individually filtered and amplified, then combined at the power amplifier for audible output. Each channel has provisions for volume control by the  $\mu P$ , or by a local/remote potentiometer. The volume control mode is selected by jumpers on the board.

#### A) SPEECH CHANNEL

The Squawk & Talk generates speech via a LSI integrated circuit U8. Commands and speech data are passed to this chip thru the PIA U7. The speech chip uses the information it receives to control an electronic vocal tract that produces a speech signal across R14. This signal contains unwanted high frequency components that are removed in a low pass filter that follows. One-fourth of U13, C19, C20, C21, R11, R15, R16, R27 and R81 form a second order low pass filter which attenuates signals above 5kHZ at the rate of 12 db/octave. This filtered speech signal is mixed with an optional off-card audio signal and is presented to the speech voltage controlled amplifier (VCA). The output of the speech VCA is fed into the power amplifier.

#### **B) SOUND CHANNEL**

Sound effects may be generated by two different sources on the Squawk & Talk module. One method uses an LSI programmable sound generator chip, U12 that is controlled via PIA U11. Commands are passed to this device which cause it to produce tones and noise by dividing down its input clock. A wide variety of sounds can be made with minimal processor interaction, however all of the waveforms produced are square wave based. The other method of sound generation employs a bus-compatible digital to analog converter, U10, driven by the  $\mu P$ . The  $\mu P$  actually constructs waveforms by controlling the DAC. This technique is used for generating sinusoidal type sound effects.

The output of the PSG, U12, is developed across R36. The harsh square waves are softened by a low pass filter before being mixed with the output of the DAC. One-fourth of U13, C31, C32, C35, R33, R37, R38, R50, R51, R52 and Q2 form second order low pass filter which attenuates signals above 3.5kHZ at the rate of 12db/octave. Transistor Q2, when switched on, via PIA U11, decreases the filter's cutoff point to about 200HZ. This feature is used for very low frequency sounds. After the output of the DAC is attenuated or amplified by the sound voltage controlled amplifier (VCA) it is mixed with the speech and then power amplified.

### C) SPEECH & SOUND VCA CIRCUITS

By employing a voltage controlled amplifier in each channel, the Squawk & Talk provides a large degree of gain control flexibility. Each VCA either attenuates or amplifies its signal according to the control voltage it is supplied with. Provisions have been made for this control voltage to be supplied from three sources for each channel. Potentiometers R69 and R70 provide a conventional, local volume control. If a remote volume capability is desired, removing R69, R70 and connecting two 1K pots in a similar fashion via J2 allows dual channel control with a three wire link without using shielded cable. Finally, by rejumpering the S & T either VCA's control voltage may be supplied by the computer.

Two accounting meters maintained in the MPU and accessible through the accounting/self-test functions are sent to the S & T every power-up. The  $\mu P$  on the S & T uses this information to initialize a 4-bit DAC for each channel which provides that channel's VCA control voltage. Thus the volume may be remotely controlled without running any wires.

The speech channel VCA consists of one-fourth of U14, C28, R13, R17, R18, R19, R28, R29, R30, CR9 and CR11. The sound channel VCA consists of one-fourth of U14, C42, R39, R40, R41, R54, R56, CR5 and CR6. Varying the cathode voltage on CR5 or CR11 changes the diode's small signal resistance. This resistance works with the input resistors R28 or R54 as a voltage divider to vary the amount of signal input to the op-amp for a control voltage range of 2.2 - 4.3VDC, the VCA's gain varies from -36 - 4.3VDC.

### D) POWER AMPLIFIER

Device U18 is an 8 watt I.C. power amplifier. It accepts audio signals from the speech and sound channels and amplifies them to an audible level suitable for an arcade. Network C29, R31 and R34 form a feedback circuit that sets the gain of the amplifier to 40db. C27 couples the signal to the speaker while blocking the D.C. component, and C30 and R35 from a high frequency shunt to prevent the amplifier from oscillating.